## **RESEARCH ARTICLE**

## **OPEN ACCESS**

## **QPSK Modulator and Demodulator Using FPGA for SDR**

Mandadkar Mukesh\*, Lokhande Abhishek\*\*, Prof. R. R. Bhambare\*\*\* \*(Department of Electronics Engineering, Pravara Rural Engineering College, Loni, University of Pune) \*\* (Department of Electronics Engineering, Pravara Rural Engineering College, Loni, University of Pune) \*\*\* (Department of Electronics Engineering, Pravara Rural Engineering College, Loni, University of Pune)

#### ABSTRACT

A software-defined radio (SDR) allows for digital communication systems to simply accept more complicated coding and modulation technologies, which is enormously vital in meeting the ever-increasing demands of the wireless communication industry. An SDR has been constructed, using the Simulink tool, and implemented on the SPARTEN-3E Field Programmable Gate Array (FPGA) development kit. The modulation scheme used in the system is Quadrature Phase-Shift Keying (QPSK). In the first step to realize the whole modulation and demodulation schemes using MATLAB Simulink. The format of a VHDL program is built around the concept of BLOCKS which are the basic building units of a VHDL design. The results showed that the proposed method can greatly improve the developing efficiency, shorten developing period and reduce costs. *Keywords* - Demodulator, FPGA, Modulator, OPSK, SDR VHDL

#### I. INTRODUCTION

The objective of this paper is to design a QPSK modem using FPGA for SDR (Software Defined Radio). In this paper the modulator and demodulator is implemented on single FPGA kit. In which mainly concentrates on QPSK modulation techniques. In QPSK, two successive bits sequence are grouped together, this reduces the bit rate of a signaling rate ( $f_b$ ) and reduces the bandwidth of the channel.

Quadrature Phase Shift Keying (QPSK) modulation ordinary used modem chips or ASICS, to implement, but those chips usually do not have sufficient programming skill and its functionality cannot easily be changed or improved in the product development process. So those chips are not suitable the situation where the parameters changed frequently. The communication system based on FPGA is easy to implement the pipeline architecture and simple to upgrade. This is a very practical approach to implement the QPSK modulator and demodulator [1].

The FPGA implementation of  $\pi/4$  QPSK modulator and demodulator is presented complete modulator and demodulator units will be modeled using VHDL and functionality will be verified using modelsim simulation tools. The code will be synthesized onto Xilinx FPGA kit. The modulator consists of various communication modules like phase calculator, I-Q mapper, frequency synthesizer, clock generator and COS-LUT. The demodulator consists of modules COS-LUT, Negative SIN-LUT, digital multiplier integrate and dump circuit and baseband differential detector. These digital modules

will be implemented as different modules and used as components in top level entities [2].

### II. THE MODULATOR AND DEMODULATOR ARCHITECTURE

Principle of QPSK modulator— in quadrature phase shift keying (QPSK), two successive bits in the data sequence are grouped together this reduces the bit rate of a signaling rate ( $f_b$ ) and hence reduces the bandwidth of the channel. QPSK Modulator— the modulator converts the input bit stream into an electrical waveform suitable for transmission over the communication channel. Modulator is used to minimize the effect of channel noise and matching the frequency spread spectrum of transmitted signal.

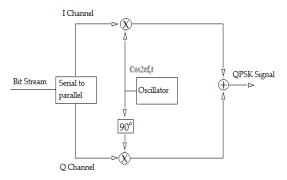

Fig (1): Block diagram of QPSK Modulator

The above fig (1) shows a block diagram of typical QPSK transmitter. The unipolar binary message stream has bit rate  $R_b$  and is first converted into a bipolar non-return-to-zero (NRZ) sequence using a unipolar to bipolar converter. The bit stream

m(t) is then split into two bit streams  $m_I(t)$  and  $m_O(t)$ (in phase and quadrature streams), each having a bit rate of  $R_s = R_b/2$ . The bit stream  $m_I(t)$  is called the" even" stream and m<sub>0</sub>(t) is called the "odd" stream. The two binary sequences are separately modulated by two carriers  $\Box_1$  (t) and  $\Box_2$  (t), which are in quadrature. The two modulated signals, each of which can be considered to be a BPSK signal, are summed to produce a OPSK signal. The filter at the output of the modulator confines the power spectrum of the QPSK signal within the allocated band. This prevents spill-over of signal energy into adjacent channels and also removes out-of-band spurious signals generated during the modulation process. In most implementations, pulse shaping is done at baseband to provide proper RF filtering at the transmitter output.

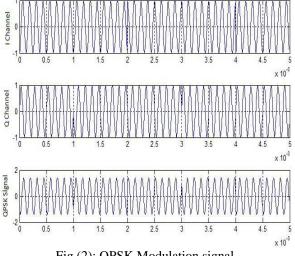

The below fig (2) shows QPSK Modulation. In this fig  $m_1(t)$  and  $m_2(t)$  are message signal, Q-ch and I-ch are Q channel signals respectively (t) is modulated signal.

## **QPSK Modulation signal:**

Fig (2): QPSK Modulation signal

**QPSK Demodulator:** The demodulation is the act of extracting the original information bearing signal from a modulated carrier wave. A demodulator is an electronic circuit or computer program in SDR that is used to recover the information content from the modulated carrier wave.

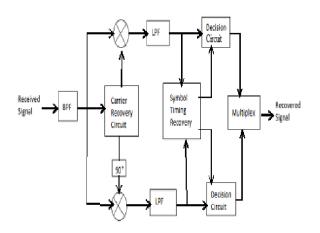

Fig (3) Block diagram of a QPSK Demodulator

The above fig shows a block diagram of a coherent QPSK demodulator. The frontend band pass filter removes the out-of-band noise and adjacent channel interface. The filtered output is split into two parts, and each part is coherently demodulated using the in-phase and quadrature carriers. The coherent carriers used for demodulation are recovered from the received signal using carrier recovery circuits. The outputs of the demodulators are passed through decision circuits which generate the in-phase and quadrature binary streams. The two components are then multiplexed to reproduce the original binary sequence.

**QPSK-Quadrature Phase Shift keying**— In QPSK two successive bits are combined this combination of two bits forms four distinct symbols. When symbol is change to next symbol the phase of the carrier changed by 45° ( $\pi$ /4 radians). The table (1) shows symbol and their phase shifts. QPSK has double bandwidth efficiency of BPSK. In mapping of I and Q NRZ format is essential. The QPSK signal is represented mathematically in below equation (1) and I/Q are defined in equation (2, 3)

| $QPSK(t) = I(t)cos(2\pi fct) - Q(t)sin(\pi fct)$ | (1) |

|--------------------------------------------------|-----|

| I= $\sqrt{2E/T} \cos [(2i-1) \pi/4]$             | (2) |

| $Q = \sqrt{2E/T} \sin \left[ (2i-1) \right]$ | $) \pi/4$ | (3) | 1 |

|----------------------------------------------|-----------|-----|---|

|----------------------------------------------|-----------|-----|---|

# Table-1 Relation between the input symbols andthe phase shifts

| Information Bits Mi, Mq | Phase Shifts $\pi$ |

|-------------------------|--------------------|

| 11                      | π/4                |

| 01                      | 3π/4               |

| 00                      | -3π/4              |

| 10                      | -π/4               |

Where T is symbol duration and is equal to twice bandwidth of bit rate period. For i=1, 2, 3, 4

The phase shifts  $\pi$  is related to input symbols mI and mQ according to the above table the in phase and in quadrature bit streams I and Q are separately modulated by two carriers and produce  $\pi/4$ QPSK waveforms given by:

$QPSK (t) = I(t)cos(2\pi fct) - Q(t)sin(2\pi fct)$ (1)

The vector I and Q carry one bit information

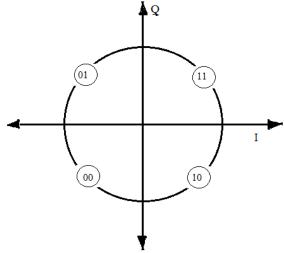

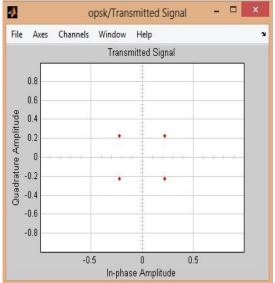

Fig (4): I-Q Mapper diagram

The above fig shows there are four symbols and the phase shifted in each symbol by  $\pi/4$  radians. Bit Error Rate— Although QPSK can be viewed as a quaternary modulation, it is easier to see it as two independently modulated quadrature carriers. With this interpretation, the even (or odd) bits are used to modulate the in-phase component of the carrier, while the odd (or even) bits are used to modulate the quadrature-phase component of the carrier. BPSK is used on both carriers and they can be independently demodulated.

As a result, the probability of bit-error for QPSK is the same as for BPSK:

$$P_b = Q(\sqrt{2E_b}/N_0)$$

However, in order to achieve the same bit-error probability as BPSK, QPSK uses twice the power (since two bits are transmitted simultaneously). The symbol error rate is given by:

$$\begin{split} P_{s} &= 1 - (1 - P_{b})^{2} \\ P_{s} &= 2Q(\sqrt{E_{s}/N_{0}}) - Q^{2}(\sqrt{E_{s}/N_{0}})^{2} \\ P_{s} &= 2Q(\sqrt{E_{s}/N_{0}}) - Q^{2}(\sqrt{E_{s}/N_{0}})^{2} \\ P_{s} &= 2Q(\sqrt{E_{s}/N_{0}}) \end{split}$$

#### III. DESIGN METHODLOGIES

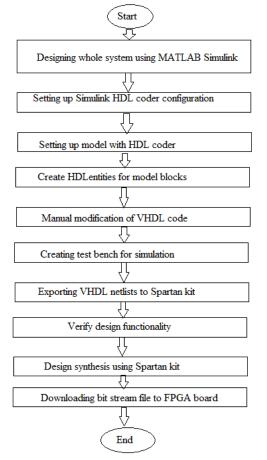

Generation of VHDL Codes for MATLAB-Simulink Models: We have designed whole system using MATLAB Simulink. AMATLAB Simulation model is describing that an enable accurate performance of complete modulations and demodulation techniques. In next step to build the basic units in FPGA Spartan kit using VHDL coding. The whole problem is split down to smaller sub parts as below

- 1 Identify the basic building blocks of various communication techniques

- 2 Design the block using MATLAB Simulink with required specification

- 3 Developing an efficient mechanism using MUX

- 4 Converting different analog block to its digital equivalent block

- 5 Getting a digital equivalent output of an analog signal by sampling quantizing

- 6 Designing all the basic units in FPGA kits using VHDL coding

The different block have to combine and communicate to develop whole system.

Design flowchart is shown below-

Fig (5) Design flow for MATLAB Simulink model using Spartan FPGA board.

Basic building blocks—The basic building block consists of different low pass filter, High pass Filter, Integrator, multiplier, Adder, Inverter, pulse

www.ijera.com

wave generator, oscillator, sine wave generator, unipolar to bipolar converter, band pass filter, multiport switches with different control signal, transfer function = 1/(S+1), comparator, Butterworth filter ,phase shifter, message signal – different wave generator, control switches.

## **IV. RESULT ANALYSES**

To ensure a high-quality product, diagrams and lettering MUST be either computer-drafted or drawn using India ink.

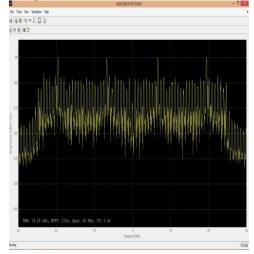

#### **QPSK signal:**

#### **QPSK transmitted signal:**

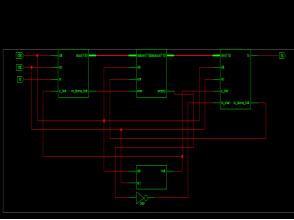

#### Synthesis RTL Schematic:

#### V. CONCLUSION

In this paper, we have presented a SDR System was successfully developed using Spartan FPGA kit. During the implementation stage, the operation of SDR was tested using MATLAB Simulink simulations, in order that the design is compiled.

#### REFERENCES

- [1] Wenmiao Song, Qiongqiong Yao, Design and implement of QPSK modem based on FPGA

- [2] A.M.Bhavikatti, Subhash Kulkarni, Uday Kalyani, FPGA implementation of  $\pi/4$  QPSK Modulator and Demodulator

- [3] Swapan K Samaddar, AtriSanyal, Somali Sanyal, FPGA based generalized architecture for Modulation and Demodulation

- [4] Gihad Elamary, Graeme Chester, Jeffrey Neasham, A simple Digital VHDL QPSK Modulator Design using CPLD / FPGAs for Biomedical Devices Applications

- [5] Mehmet SÖNMEZ and Ayhan AKBAL, FPGA based design using VHDL transmission performance analysis of BPSK and QPSK Modulators

- [6] Anton S. Rodriguez, Michael C. Mensinger, Software-defined Radio Using Xilinx

- [7] Dr. Hikmat N. Abdullah, Hussein A. Hadi, Design and implementation of FPGA based SDR using Simulink HDL coder

- [8] Hugo Santos, Mario Vestias & Helena Sarmento, FPGA prototype of a DCM demodulator using the Matlab

- [9] Professor Fred J. Looft & Dr. R. Scott Erwin, Modular FPGA-Based Software Defined Radio

- [10] Popescu SO, Gontean AS, Ianchis D, Implementation of a QPSK system on FPGA

- [11] Michal Kovac, BPSK, QPSK Simulation model

- [12] Rajesh R. Bhambare, Dr. Rajeshree D. Raut, A survey on Digital Modulation Techniques for SDR Applications

- [13] Teena Sakala, Divya Jain, Sandhya Gautam, Implementation of Digital QPSK Modulator By Using VHDL/MATLAB